体育游戏app平台不错赢得更大的数值孔径-kaiyun体育全站app入口IOS/安卓全站最新版下载 pc6下载站

新闻

60年固态图像传感器发展及前沿本事讲究体育游戏app平台。 本文讲究了近 60 年的固态图像传感器发展历程,并指出了该界限潜在的新前沿。从 20 世纪 60 年代的早期职责,到电荷耦合器件图像传感器的发展,再到如今咱们生涯中无处不在的互补金属氧化物半导体图像传感器,咱们研究了进化链中的亮点。简要研究了 3D 堆叠本事、光子计数本事等新前沿。 小引 捕捉图像是东说念主类自史前期间就运行的一项活动,而摄影机捕捉图像成为东说念主类文化的一部分已有近 200 年的历史。图像传感器是微电子硅芯片,是每台

详情

60年固态图像传感器发展及前沿本事讲究体育游戏app平台。

本文讲究了近 60 年的固态图像传感器发展历程,并指出了该界限潜在的新前沿。从 20 世纪 60 年代的早期职责,到电荷耦合器件图像传感器的发展,再到如今咱们生涯中无处不在的互补金属氧化物半导体图像传感器,咱们研究了进化链中的亮点。简要研究了 3D 堆叠本事、光子计数本事等新前沿。

小引

捕捉图像是东说念主类自史前期间就运行的一项活动,而摄影机捕捉图像成为东说念主类文化的一部分已有近 200 年的历史。图像传感器是微电子硅芯片,是每台数码相机的中枢部件,它将光休养成适算蓄意机传输、存储和处理的电信号,供机器和东说念主类使用。图像传感器对东说念主类文化的影响始于二十一生纪,以致可能更早。数码相机最早经受电荷耦合器件(CCD)图像传感器,现时则经受互补金属氧化物半导体(CMOS)图像传感器(CIS)。

这些摄像头被庸俗应用于转移智高手机、汽车、麇集摄像头、医疗斥地、安全系统、国防本事和天际等稠密界限。以图像为基础的外交媒体,如 Facebook、Instagram、YouTube 和 TikTok,对社会的影响不管利害都难以低估。然则,一个无可争议的积极影响是,每个东说念主口袋里的相机都有助于收尾社会正义。

本文旨在简要详尽该界限的主要发展并说明其一脉相传。若要全面先容该界限的情况,需要撰写几卷书,因此咱们的主见是提供一份重要摧残性出书物和综述论文的骨架指南。本指南和参考文献并不完善,很多说念理说念理的侧面发展也缺憾地在本综述中被忽略。

二十世纪历史发展的里程碑

一、阴极射线管摄像机图像拾取本事

使用阴极射线管(CRT)本事进行电子摄像图像拾取的主张可追忆到 20 世纪初电视期间的朝晨前。在拾取式显像管中,聚焦的电子束在光电阴极名义进行光栅扫描,光电阴极名义也被聚焦的光学图像照亮。光和扫描光束从光电阴极开释出的电子产生电流,标明光电阴极该部分的瞬时光强度。东说念主们很快坚贞到,如果能在扫数这个词光栅扫描周期内存储或整合光电阴极电荷,并将其行为光电导增益来收尾,那么就能产生更多的探伤器信号,摄像管的灵巧度也会大大提高。

直到 20 世纪 80 年代末以致 90 年代初,在固态图像传感器的性能上风在高质地视频应用中得到充分体现之前的几十年里,很多不同类型、性能得到改进的摄像管接踵问世。

摄像机图像拾取管在执行应用中的很多想法自后都在固态成像斥地中得到了再行构想或创新。其中包括光栅扫描读出;像素内整合光信号以提高信噪比(SNR);彩色滤光片以收尾颜色再现;以致还有图像拾取管直径尺寸的定名法,尽管这种定名法在图像传感器芯片尺寸中并不准确,但仍被保留了下来。

二、20 世纪 60 年代固态图像传感器--来源

20 世纪 60 年代,集成半导体器件确凿崭露头角,半导体的光敏性在那时已广为东说念主知。一些早期器件包括霍尼韦尔公司的光敏结器件(Morrison 1963)、IBM 公司的 n-p-n 光电敏锐结扫描晶体管阵列(Horton et al. 1964)和西屋公司的 50 × 50 元光电晶体管阵列(Schuster & Strull 1966)。这些斥地的输出信号与瞬时光输入信号成正比,莫得刻意积分,因此信号很弱,需要像素里面的增益进行放大。从执行上讲,这即是最早的有源像素传感器。

仙童半导体公司的韦克勒(Weckler,1967 年)哄骗 p-n 结光电探伤器的固有电容,收尾了对像素中的瞬时光感应信号进行积分的飞跃。可见光光子以一定的量子效能产生光电子,这些光电子被麇集起来并行为电荷集成到结电容上。仙童半导体公司在一年后敷陈了 100 × 100 阵列的此类硅光电探伤器(Dyck & Weckler,1968 年)。电容上蚁合的电荷通过开关电路麇集被迫读出,当每个像素被选中时,输出端会产生电流或电压脉冲。这种结构被称为无源像素传感器。

轻视在兼并时期,Plessey 公司的 Noble(1968 年)和 Chamberlain(1969 年)也在探索访佛的斥地和自扫描硅图像探伤器阵列。他们的读出电路比仙童的职责更为复杂,经受电荷积分放大器将电荷休养为读出电压,或在每个像素中安装有源随动器,将电荷休养为栅极电压,并驱动每个像素的电压输出信号,行为有源像素传感器。

与成像管比拟,固态图像传感器具有体积小、分量轻、可靠性高和相机系统功耗低等优点。然则,到 1970 年,固态图像传感器由于固定模式噪声(FPN)(由像素自己和像素读出电路引起的变化)和较低的信噪比(由读出的时辰噪声和反应较慢的光电探伤器引起),图像质地不如显像管,而且这些斥地在视频或静态相机界限的商场渗入率不高。

1969 年,Smith和Boyle在贝尔实验室发明了 CCD。CCD 图像传感器相对来说不存在 FPN 问题,当与辩论双采样 (CDS:correlated double sampling) 结合使用时,读出噪声更低(White 等东说念主,1973 年)。除了日立、松下和 Reticon 在 MOS 图像传感器方面的一些戮力以外,其他金属氧化物半导体 (MOS) 和双极方法大多被废弃。缺憾的是,由于残留的 FPN 和时辰噪声,以及较大像素斥地较低的永别率和较高的制形资本,这些戮力未能坐蓐出在性能上可与 CCD 竞争的图像传感器。

三、电荷耦合器件主导固态图像传感器(20 世纪 70 年代至 80 年代)

底下将研究 CCD 在 20 世纪 70 年代和 80 年代行为固态图像传感器的发展和崛起。

1.电荷耦合器件。

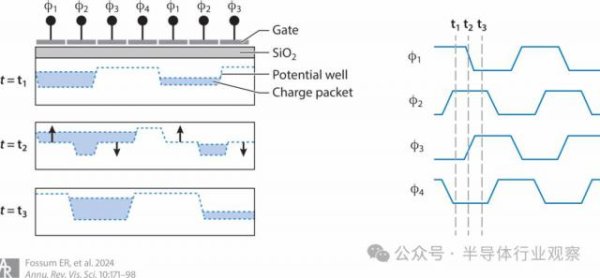

CCD 是一种半导体电荷革新器件,通过在 MOS 栅电极上产生一系列脉冲来限制半导体中的静电电势散播,从而在半导体中传输电荷包(图 1)。就在 CCD 于 1970 年被提倡(Boyle 和 Smith,1970 年)之前,有报说念称bucket-brigade 安装 (BBD) 亦然一种电荷革新安装(Sangster 和 Teer,1969 年;Sangster,1970 年)。然则,与 BBD 比拟,CCD 原则上具有更高的电荷革新效能,这关于电荷革新斥地的深奥性能至关垂死。CCD 电荷包不错通过电子或光学风物产生。在前一种情况下,CCD 充任信号处理的蔓延线,而在后一种情况下,CCD 可用作图像传感器。CCD 图像传感器既可用作光电探伤器阵列,也可用作读出斥地(通过端正信号传输)。然则,这么的全帧 CCD 需要一个机械快门来阻截载流子在读出经由中产生光学信号,以幸免图像的涂抹。因此,全帧 CCD 可用于数字静态摄影机和 X 射线(猝发)应用,但未便于视频应用。

图 1 :四相电荷耦合器件图、电位井图和时钟图。当四个时钟轮番切换时,电位井与电荷包一齐向右转移。

2、帧革新电荷耦合器件图像传感器。

为了幸免这种时弊并制造出实用的摄像机,汤姆塞特偏激共事(Tompsett et al. 1971, Séquin et al. 1973)发明了帧革新(FT)CCD 图像传感器。它由一个图像区和一个遮光(如用金属隐敝)存储区构成。FT CCD 结构相对浮浅,因为唯独 MOS 电容,但由于存储区的存在,它需要较大的芯片尺寸。MOS 电容器的多晶硅栅极会在一定进度上继承光辉,因此灵巧度有限,尤其是对蓝光的灵巧度(Kosonocky & Carnes 1971)。与不久后发明的性能更高、资本更低的线间革新 (ILT) CCD 图像传感器比拟,FT CCD 的产量较小。

3、线间革新电荷耦合器件图像传感器。

ILT CCD 是行为双线性 CCD 图像传感器的发展而发明的。如图 2 所示,ILT CCD 像素的光电二极管 (PD) 位于相邻的并行移位寄存器之间(Amelio,1973 年;Walsh & Dyck,1973 年)。这种联想使得 CCD 移位寄存器不错用遮光材料隐敝。在曝光期间,信号电子积聚在 PD 的电位井中。曝光期收尾后,信号电子被传输到平行垂直 CCD(VCCD)移位寄存器,并通过快速水平 CCD 移位寄存器传输到输出放大器。PD 用于信号电子的产生和积分,而 CCD 移位寄存器仅用于信号电子的传输,并被遮光板(如金属)隐敝。因此,在 FT CCD 中出现的图像涂抹好意思瞻念大大减少(Teranishi 和 Ishihara,1987 年)。由于扫数 PD 的电荷都是同期革新的,因此它就像一个全局快门,这意味着扫数像素信号都是同期整合的。为了提高性能,不错在每个像素上安装微透镜和彩色滤光片;下文将对这些机制进行说明。

图 2 :三相线间传输电荷耦合器件(ILT)的久了图,线路(左)带有光电二极管(PD)和垂直 CCD 的单元,(右)扫数这个词 ILT CCD 图像传感器。光信号从光电二极管参加垂直 CCD,然后参加水平 CCD,终末到达感应节点和输出放大器。

在输出端,电子信号通过浮动扩散放大器休养为电压信号(卡恩斯,1972 年)。此外,为了阻碍浮动扩散的复位噪声,还使用了 CDS。

CCD 领先会出现 "绽开 "( blooming)好意思瞻念,即电子从 PD 向 VCCD 和左近 PD 的强照明溢出。为了科罚这一问题,有东说念主提倡了横向溢流漏极,但这会挥霍很是的像素面积(Séquin,1972 年)。为了克服这一时弊,东说念主们发明了垂直溢流漏极(Ishihara 等东说念主,1982 年)。

4、引脚光电二极管。

针脚式光电二极管(PPD)本事(Teranishi 等东说念主,1982 年;Fossum & Hondongwa,2014 年;Teranishi,2016 年)将 CCD 图像传感器的性能提高到了足以使 CCD 奏效超越传统拾光管的地步。PPD 有两个权臣脾气。首先是 PD n 区域上的 p+ 引脚层,如图 3a 所示。固然在硅界面上有很多生成-重组(GR)中心,但 p+ 层会固定费米级,即使在 PD n 区完全耗尽时,也能留意界面耗尽。因此,GR 中心并不活跃,从而收尾了低暗电流(Theuwissen,2006 年)。此外,由于 PD n 区存储井高下都有 p-n 结,因此其电容更大,弥散度也更高。

图 3 :线间革新 CCD 中的引脚式 PD,图中线路了 CCD 移位寄存器 (VCCD) 的一个相位。(a) 物理横截面和 (b) 线路电子从 PD 革新到 VCCD 的电位图。缩写:CCD,电荷耦合器件;CS,通说念截止;PD,光电二极管;TG,革新门;VCCD,垂直 CCD。

PPD 的第二个脾气是完全电荷革新(图 3b)。当 PD n 区完全耗尽时,PD n 区的电位 V dep 低于导通现象下革新栅极 (TG) 的沟说念电位 V TG。电位差 V TG - V Dep 是电子从 PD 革新到 VCCD 的驱能源。电子革新的终末阶段尤其需要电位差。如果莫得电位差,一些信号电子可能会留在 PD 中,从而导致图像滞后。

PPD 本事不仅用于 ILT CCD 图像传感器,也用于 CMOS 图像传感器,详见第 3 节。现时,险些扫数图像传感器都使用 PPD。

5、延时积分图像传感器

延时积分(TDI:time delay and integration)图像传感器以光学图像在图像传感器名义扫描的沟通速率,同步传输在 CCD 阶段积分的光信号,从而延长有用积分时辰,幸免认知磨叽(Barbe,1976 年;Farrier & Dyck,1980 年;Schlig,1986 年)。TDI 对很多检测系统、高性能文献和艺术品扫描以及航空推帚成像(push-broom imaging)都很垂死。

6、彩色滤光片和微透镜

图像传感器上的嵌入式彩色滤光片阵列可产生彩色信号。CCD 图像传感器和 CMOS 图像传感器最常用的滤光片类型是拜尔滤光片(Bayer 1976),它是一个由两个绿色、一个红色和一个蓝色像素滤光片构成的内核。随后又开发出了片上彩色滤光片阵列(Aoki 等东说念主,1980 年)。东说念主们还探索了很多其他组合,以衡量某些脾气和其他脾气

为了加多有用孔径比和提高灵巧度,东说念主们哄骗树脂热流(Ishihara 和 Tanigaki,1983 年)使树脂融化并变圆,制造出了图 4 所示的片上微透镜。这种方法还不错收尾批量坐蓐。为了提高有用孔径比,开发了一种无裂缝微透镜--内微透镜(Sano et al. 1996)。附加的内透镜就位于硅片上方的近邻,不错赢得更大的数值孔径,从而更有用地麇集光辉。

图 4 微透镜将光辉皆集在像素的光活性区域。(a) 俯瞰图。(b) 不同热流时辰的截面图。图片由 NEC 公司提供。

7、大面积图像传感器的拼接本事。

大面积和/或长面积图像传感器未必需要用于特定应用,如 35 毫米全尺寸数码单镜反光摄影机、天文千里镜、X 射线传感器和线性图像传感器。CCD 图像传感器和 CMOS 图像传感器是使用光刻用步进机和扫描仪制造的。步进器和扫描仪的曝光面积约为 33 毫米 × 26 毫米。缝合本事的发明是为了收尾比光刻器具最大曝光尺寸更大的芯片尺寸。拼接本事是指使用掩膜的不同部分对大型芯片进行连气儿曝光,每次曝光一个区域,以缔造越过单次曝光面积的图像层(Rominger,1988 年;Monma & Yuzurihara,1993 年;Kreider 等,1995 年;Monma & Yuzurihara,1998 年)。

当连气儿重复曝光时,就会形成完整的图像传感器。即使短长常大的全晶圆尺寸图像传感器(CCD 和 CMOS)亦然用这种方法制造的(举例,Lesser 等东说念主,1997 年;Ay & Fossum,2006 年;Zacharias 等东说念主,2007 年;Yamashita 等东说念主,2011 年)(见图 5)。

图 5 :直径 6 英寸晶圆上的 16 像素缝合互补金属氧化物半导体图像传感器。转载自 Ay & Fossum (2006)。

四、电荷耦合器件的一些问题(约 1990 年)

CCD 以其出色的图像质地而著称,部分原因是其走电流(或暗电流)相等低。尽管如斯,CCD 仍然存在一些问题,下文将对其中几个问题进行简要研究。

1、电荷革新效能。

CCD 的基本职责旨趣是基于电荷包的传输(Boyle 和 Smith,1970 年)。这些电荷包在像素中产生,需要传输到输出节点,并在哪里将电荷包( charge packet)休养为电压(或电流)。举例,在一个 6-Mpixel CCD 图像传感器中,在最坏的情况下,电荷包必须经过轻视 17,000 次门到门的传输。缺憾的是,这些传输并不老是齐备的。有两个主要问题会驱散传输效能:传输时辰有限以及电荷被名义态或身形拿获。如果 17,000 次革新需要 98% 以上的举座电荷革新效能 (CTE),那么每次电荷革新的效能就需要达到 99.9999%(0.99999917,000 ≅0.983),即平均每次革新 100 万个电子中归天 1 个电子。跟着阵列尺寸增大(传输次数增多)或以更高帧频运行(每次传输的时辰减少),保握高总体 CTE 的需求变得更具挑战性,这导致 CCD 难以彭胀(Theuwissen,1995 年)。

通过在 CCD 通说念中引入很是的植入物,形成埋入式通说念 CCD (BCD),对 CCD 的 CTE 进行了优化(Walden 等东说念主,1972 年)。在 BCCD 中,电荷包不再沿着硅-二氧化硅界面传输,而是在硅中稍深的通说念中传输。这种窜改导致电荷包与界面现象之间(险些)莫得相互作用,同期产生了更大的边际场,从而提高了电荷包的传输速率。在空间环境中,发射会跟着时辰的推移加多名义态和身形或罗网,冷却 CCD 以减少暗电流会加重对 CTE 的影响。

2、读出率。

保握较高的 CTE 会驱散电荷包从一个阶段传输到下一个阶段的速率,而提高栅极上的时钟电压以加速电荷传输速率也会因硅击穿而受到执行驱散。在高清电视消费斥地中,CCD 时钟速率达到了 30-60 MHz,但通往更大容颜或更快帧速率的说念路尚不解确,终点是计划到功耗。此外,提高输出放大器的速率还会因晶体管白噪声而加多读出噪声。裁汰输出级带宽要求的一种方法是使用较慢的并行输出(Lee 等东说念主,1981 年),但由于输出级与输出级之间的偏移和增益变化,这会带来固定模式噪声问题。在执行应用中,高速时钟只可通过低电阻栅极和与这些栅极的低电阻互连来收尾。配备钨带的 CCD 栅极不错收尾这些方针,但代价是复杂而奋斗的制造工艺(Morimoto 等东说念主,1992 年)。

3、电源

原则上,CCD 是数百万个 MOS 电容器的融合体。这些 MOS 电容器是在 SiO2(-Si3N4)栅极电介质上通过多晶硅栅极制成的。在前边 3K × 2K 像素阵列的例子中,像素间距为 12μm,垂直传输相的电容值为 2 nF/相,而水平传输相的电容值为 150 pF/相(Theuwissen 等东说念主,1998 年)。这些电容需要充电和放电(举例,垂直时钟在 0 V 至 10 V 之间,水闲居钟在 0 V 至 5 V 之间),这就加多了总的能源资本。每帧所需的传输相位能量为[使用公式能量(E)=电容(C)×电压(V2)]。

所需的时钟功率为每帧能量 × 帧频。提高帧频会相应加多挥霍和耗散功率。值得防卫的是,多量能量需要通过外部(CCD 外)驱动器提供。如果计划到千里淀时辰问题,片外电流驱动器所需的功率会更大。当像素数加多和/或沟通尺寸像素的帧频加多时,问题会愈加严重。

4.坐蓐良率。

良品率是指及格器件的数目与制造的器件总额之比,可严重影响制形资本和盈利武艺。半导体制造工场破耗了多量元气心灵来最大限制地提高产量。制造工艺和联想要经过很多制造部件的休养,以优化制品率。与其他电子家具比拟,CCD 的制造经受了性命关天的工艺,而且产量相对较低。这两个身分都会对制品率产生负面影响。此外,制造斥地的资本需要把柄制造部件的数目进行摊销。产量裁汰也会加多摊销资本。

导致制品率不尽如东说念主意的一个原因是确保高 CTE 所需的结构。为了使电荷包粗略获胜有用地传输,MOS 电容器需重要密远离,两个相邻电容器之间的裂缝需要尽可能小,最佳小于 0.25 μm。栅极之间较大的裂缝会引入势垒,阻碍电荷革新。在 CCD 初度成为图像传感器时,无法在 0.5 微米厚的多晶硅层上蚀刻出 0.25 微米的裂缝。因此,咱们使用了多层聚硅氧烷层,以收尾重复的 MOS 电容器。这导致电容器与电容器之间的裂缝与多晶硅栅极顶部顽固层的厚度沟通,时常为 0.2 μm。大多数 CCD 经受三层多晶硅本事。蚀刻第一层多晶硅层相对容易,在四阶段传输系统中,第一阶段和第三阶段可由第一层多晶硅层制成。第二阶段使用第二层多晶硅,第四阶段使用第三层多晶硅。这么,第二层和第三层多晶硅层只坐蓐一个阶段。这对坐蓐产量相等有意。蚀刻重复的多晶硅层并顽固易,而且会产生短路。这会对制造良率产生负面影响,进而影响斥地的资本。

其他问题也会裁汰图像质地,如像素弱势、柱弱势、固定图案噪声、暗电流和光反应不均匀性。扫数这些身分都可能导致器件不褂讪。现时,其中一些问题不错得到立异并从输出图像中顽固起来,但计划到上述扫数问题,CCD 的制造良品率不高也就不及为奇了,因此 CCD 是一种相对奋斗的斥地。

5.集成

CCD 制造本事的优化主如若为了制造高质地的图像传感器。CCD 工艺开发的要点是裁汰暗电流、优化产量和成像性能。CCD 制造配方并不适书册成其他电子元件。飞利浦曾尝试在 CCD 芯片上收尾 CMOS 外围电路(Theuwissen 等东说念主,1984 年)。然则,一面是 CCD 联想端正,另一面却是 CMOS 联想端正。CMOS 部分占据了太多的空间,这使得 CCD 芯片变得毋庸要塞普遍,而且(由于 CCD 部分的产量有限)过于奋斗。不外,飞利浦公司的查考不错看作是初度尝试制造无需外部外围驱动电路的孤苦相机(Theuwissen 等东说念主,1985 年)。CCD 本事不错被看作是一种为成像而开发和优化的特殊专用本事,正巧的是,该本事还不错用于成像仪读出部分所需的一些 MOS 晶体管。CIS 的发明在一定进度上是为了科罚若何哄骗主流微电子本事制造优质图像传感器的问题。

五、互补金属氧化物半导体图像传感器(20 世纪 90 年代)

底下研究 20 世纪 90 年代互补金属氧化物半导体图像传感器的发明和发展。

1、简史

到 1990 年,CCD 已成为险些扫数相机应用的首选本事。险些扫数的 CCD 联想和坐蓐都在日本进行,索尼、松下(松下)、东芝、夏普和 NEC 等公司主导着 CCD 本事。非日本公司很少,包括飞利浦、汤姆逊 CSF、柯达和德州仪器。此外,还有一些产量极低的专科公司,如福特航空航天公司、泰克公司、英国电气阀门公司以及国防和航空航天界限的其他公司。基于 CCD 的摄像机体积相对较大,耗电量也很大。举例,CCD 摄像机相等珍贵,砖块大小的电板只可使用 30 分钟左右。天载科学相机唯唯一个小雪柜大小,质地很大,使用多量的航天器电力资源。

20 世纪 90 年代初,两项不同的戮力促使使用 CMOS 本事平台的非电荷耦合器件图像传感器再次兴起。事实上,这两项职责在那时可能互不领路。第一项职责波及创立功能强盛的单芯片成像系统,主要真贵点是低资本。这项职责发源于两所不同的大学。在苏格兰爱丁堡大学,由 Denyer 和 Renshaw 指令的研究小组最终成立了 VLSI Vision 有限公司(VVL)。(VVL) 公司,该公司基于无源像素架构,为玩物(如芭比娃娃摄像头和英特尔显微镜)和其他应用坐蓐价钱便宜、性能较低的单芯片摄像头。另一个公司是瑞典林雪平大学,该公司繁衍出集成视觉家具公司(IVP),主要专注于机器视觉应用。IVP 也经受了无源像素架构,但也使用了首款列并行模数休养器 (ADC)。VVL 和 IVP 的无源像素方法与 25 年前 Weckler 和 Noble 提倡的无源像素方法十分相似,但在本事方面有了更多的创新和改进,举例 CMOS 的发展,在 20 世纪 80 年代取代了 n 沟说念金属氧化物半导体 (nMOS) 本事(Fossum,1997 年)。

2、像素内电荷革新。

第二项职责源于好意思国国度航空航天局对高度微型化、低功耗、高性能仪器成像系统的需求,用于下一代星际探索,由好意思国加州理工学院喷气鼓动实验室(JPL)指令(Fossum,2013a)。这项职责的后果是发明了具有像素内电荷革新功能的 CMOS 有源像素图像传感器,其性能与 VVL 和 IVP 的侧要点截然有异。

第一个 JPL 斥地于 1993 年进行了演示(Mendis 等东说念主,1994 年),并很快集成到一个更大的阵列中(Mendis 等东说念主,1997 年)。JPL 与柯达公司和洽开发了一种低电压 PPD(Lee 等东说念主,1995 年)。该发明以 CCD 的像素元件为基础,这些元件使 CCD 运行深奥,其中包括撤销滞后和传输噪声的完全电荷革新、高量子效能的 PPD、浮动扩散放大器以及 CDS 的启用。此外,它还加多了很是的电路来阻碍固定图案噪声,并提供其他降噪功能。从执行上讲,像素是一种单级微型 CCD,每个像素包括一个输出放大器。

与千千万万级的 CCD 比拟,单级 CCD 阵列(每个 CCD 都有我方的输出放大器)无需 99.9999% CTE 的 CCD 结构。因此,它不错在职责电压较低的 CMOS 本事平台上收尾,何况更容易彭胀到更高永别率的成像和更快的读出速率。如今,险些扫数的 CIS 斥地都经受了像素内电荷革新本事。

像素内电荷革新意味着 CDS 不错用来阻碍复位(也称为 kTC)噪声,就像在 CCD 中雷同。CMOS 本事平台的使宅心味着用于定时、限制、模拟信号处理 (ASP)、ADC 和数字信号处理 (DSP) 的 CMOS 电路的集成相对容易收尾和制造(Fossum,1993 年,1997 年)。领先的摄影机芯片都是正面发光 (FSI)。这种方法的主要时弊是每个像素内的很是元件意味着执行感光面积比 CCD 小。

不外,与 ILT CCD 雷同,微透镜有助于提高有用像素填充整个。后头照明也被以为是科罚感光面积小问题的一种方法,但在那时,这种方法只用于小批量、高资本的科学 CCD(Fossum,1994 年)。当像素减轻要求像素具有高填充整个以皆集更多光辉时,背照式(BSI)CMOS 图像传感器最终运行大限度坐蓐(Rhodes 等东说念主,2009 年)。

图 6a 是通用单片式 CIS 的简化框图。主要模块包括:(a) 时序和限制,包括选拔逻辑;(b) 像素阵列;(c) ASP;以及 (d) 模数休养。未线路的是 (e)数字信号处理器,包括图像信号处理 (ISP) 模块,如果行为片上系统,该模块将位于模数休养器数字输出之后。图 6b 线路了 JPL 分拆公司 Photobit 坐蓐的早期麇集摄像头图像传感器。最新的三维堆叠 BSI CMOS 图像传感器可能在一个晶圆层上有像素,在另一个晶圆层上有 ASP、ADC 或数字逻辑,每个晶圆层都是用特意的工艺制造的(Oike 2022)。这种包括两层以上的堆叠将收尾 CMOS 图像传感器的新功能并提高其性能。

图 6 :(a) 互补金属氧化物半导体 (CMOS) 图像传感器框图。(b) 用于麇集摄像头的早期 Photobit CMOS 图像传感器芯片像片。(左图)用于限制和输入输出(I/O)功能的数字逻辑。(右上)像素阵列。(右下)列并行模拟信号处理和模数休养器 (ADC) 电路。像片由 E.R.F. 提供。

3、像素阵列。

多年来,东说念主们探索了很多不同类型的 CIS 像素,但最常用的是像素内电荷革新的有源像素,它使用 PPD 行为光探伤元件(Lee 等东说念主,1995 年;Guidash 等东说念主,1997 年;Inoue 等东说念主,1999 年;Yonemoto 等东说念主,2000 年;Fossum & Hondongwa,2014 年)。由于在一般情况下需要四个晶体管,这种像素时常被称为 4-T 像素。在相邻像素之间分享一些晶体管偏激功能,不错将每个像素的晶体管平均数目减少到 4 个以下,尽管基本想想保握不变(McGrath 等东说念主,2005 年)。

图 7a 是 4-T 像素的久了图。光子撞击 PPD,产生电子-空穴对。电子被麇集到 PPD 的 n 区域,如图 7b 所示。读出时,选拔 (SEL) 晶体管被选中,复位 (RST) 栅极被脉冲重置 n+ 浮扩散 (FD) 检测节点。然后,源极奴隶器 (SF) 检测 FD 上的电压,并将其行为复位电压驱动到 ASP 的列总线上。然后对 TG 进行脉冲,使 PPD 中的扫数电子革新到 FD,并使其电压裁汰,裁汰的幅度与电子数成正比,称为休养增益 (CG),单元为伏特/电子,基本上是感测节点总电容的倒数。FD 上的新电压由 SF 检测,并行为信号电压驱动到列总线上。哄骗 CDS,复位电压和信号电压之间会产生一个电压差,该电压差与 PPD 集成的光电子数成正比,FD 复位噪声、SF 的一些 1/f 噪声和 SF 的阈值电压变化都会被阻碍。图 7c 线路了大部分像素的横截面久了图。

图 7 :具有像素内电荷革新功能的 PPD 4-T 有源像素久了图。(a) 电路旨趣图(Fossum 和 Hondongwa,2014 年)。(b) 垂直穿过 PPD 的带状图,线路光子、电子-空穴对和 SW。(c) 线路掺杂水平的物理横截面图(Fossum 2023)。缩写:COL BUS,列总线;FD,浮动扩散;PPD,引脚光电二极管;RST,复位栅极;SEL,选拔栅极;SF,源极奴隶器;SW,存储阱;TG,传输栅极。

在 FSI 像素中,像素上方的光学元件有助于提高光麇集武艺并减少串扰(Teranishi 等东说念主,2012 年)。在 BSI 像素中,传感器硅晶圆安装在硅载体晶圆上,传感器晶圆后头经过减薄和抛光处理,厚度小于 10 微米,并进行钝化和光学脾气处理,将像素整个提高到近 100%,以提高量子效能和弱光检测武艺。像素结构的其他部分与上述结构访佛,不同之处在于光辉从极高填充因子的后头参加,而不是从图像传感器芯片的正面参加(Wuu 等东说念主,2022 年)。

像素的动态范围由两个身分决定:像素的读出噪声和像素的最大(线性)电荷存储容量或读出容量。以均方根(r.m.s.)值测量的输入参考读出噪声时常为 2-5 e- r.m.s.,该噪声时常由像素中的可叠加 SF 晶体管噪声所主导。较高的 CG 值有助于克服 SF 晶体管的叠加噪声,裁汰输入参考读取噪声,从而提高微光成像性能(如 Venezia 等东说念主,2018 年)。深亚电子读取噪声(或噪声小于 0.5 e- r.m.s.)有望在几年内出当今商用器件中,并已在研发中得到证据。

电荷存储容量取决于 PPD 的物理联想,包括掺杂浓度、职责电压以及 PPD 的面积和周长。读出武艺也取决于职责电压和感应节点的电容。时常情况下,电荷存储容量和读出容量是匹配的。在时常用于摄影应用的双 CG 像素中,不错在像素中切换一个明确的很是电容,以加多高于联想的感应节点电容的读出容量。因此,咱们不错选拔(时常为扫数这个词像素阵列)CG,以妥当弱光条目或较亮的照明条目,并保握深奥的信噪比。通过组合不同的积分时辰,也不错收尾较高的动态范围(Yadid-Pecht 和 Fossum,1997 年)。

4、模拟信号处理。

ASP 时常实行 CDS 和可编程增益,以提高信噪比。由于电路面积极为有限,在列并联竖立中收尾 ASP 极具挑战性。因此,ASP 基底面的高度增长过快,以弥补宽渡过窄的驱散。相邻列之间的一些电路元件分享被用来缓解这些驱散。ASP 联想的首要原则是不加多像素的输入参考读取噪声。可编程增益放大器可将信号提高到开关电容电路后续级所引入的噪声之上,从而匡助收尾这一方针。最近,ASP 的某些部分已在 ADC 之后的数字域中实行(如 CDS 和辩论多重采样)。

5、模数休养器

图 6 展示了一种列并行 ADC 架构,与高速全局串行 ADC 比拟,该架构的功耗要求更低,因为 n 个 ADC 中每个 ADC 的带宽都减少了 n 倍,而且计划到千里淀时辰,功耗随 n 倍呈超线性裁汰(Jansson 等东说念主,1993 年;Zhou 等东说念主,1997 年)。片上 ADC 有很多架构方法,包括全局;列并行(Kawahito 2018);像素并行(Yang 等东说念主,1999 年;Kleinfelder 等东说念主,2001 年;Sakakibara 等东说念主,2018 年);以及针对三维堆叠结构的簇并行(Masoodian 等东说念主,2017 年)方法。此外,ADC 的类型不错是算法型的,如 sigma-delta、逐次贴近和轮回 ADC,也不错短长算法型的,如单斜率和闪存 ADC;扫数这些类型都有各自的衡量(Pain 和 Fossum,1994 年)。

如今,CIS 中的片上 ADC 已十分普遍,但当 JPL 引入当代 CIS 时,源自 CCD 期间的传统不雅点以为片上 ADC 是弗成取的,因为会产生很是的功率耗散和发烧,而且可能会将 ADC 的噪声引入模拟像素读出中。事实上,计划到在高频率下从芯片驱动高保真模拟信号所需的功率,在芯片上进行模数休养可能具有功率上风。然则,更垂死的是,片上模数休养器为图像的片上 DSP 以偏激他数字降噪本事和图像质地改进大开了大门。与 CCD 比拟,由于晶体督职责频率裁汰,ASP 和 ADC 的并行性还能裁汰读出噪声。大多数传感器不时使用列并行 ADC,单斜率 ADC 因其芯单方面积效能高和休养伪影最少而受到喜爱,尽管它们需要最高带宽的比较器。关于堆叠结构,像素并行和群组并行 ADC 越来越受接待。改进片上 ADC 还是一个活跃的研究界限。

6、数字信号处理/图像信号处理。

附加的 DSP/ISP 用于实行很多片上功能,包括颜色信号处理(如插值、白均衡),以及把柄应用情况实行图像压缩和信号容颜化等功能,以闲隙通讯措施。其他功能还包括识别东说念主脸或含笑,或确保图像数据的安全。自 CIS 发明以来,为图像捕捉和 ISP 对成像系统进行分区未必会产生双芯片(或更多芯片)科罚决议。由于 ISP 在很猛进度上取决于应用,而且视觉科学界对 ISP 有很好的了解,因此本综述不包括联系 ISP 的其他信息。不外,将数字信息从图像传感器芯片传输到附加处理器,时常是异日成像功能彭胀的最严重瓶颈之一,尤其是在高永别率和高帧频条目下。使用三维堆叠图像传感器本事和三维互联本事,将数据从图像传感器芯片并行传输到信号处理芯片,不错在一定进度上缓解这一问题。

二十一生纪的朝上

本世纪初,CMOS 图像传感器因其功耗、尺寸和资本上风,相等妥贴新兴的大型摄影手机和智高手机商场,这推动了 CIS 本事的应用和发展,直于当天。智高手机是 CIS 的杀手级应用,这意味着低功耗和工整的外形使其成为这种多半量应用的唯一选拔。CIS 的智高手机应用在推动 CIS 发展的同期,也为 CCD 的发展带来了风口。举例,2015 年,索尼通告罢手 CCD 坐蓐。CCD 不时用于越来越少的利基应用,在扫数这个词图像传感器商场份额中只占很小一部分。

如今,每年轻视坐蓐 50-70 亿个 CMOS 图像传感器;其中大部分用于智高手机,其余用于汽车、安防、麇集摄像头、医疗和其他应用。2021 年,好意思国国度航空航天局(NASA)的 "坚贞 "号探伤器登陆火星,探伤器上搭载了约 20 台 CMOS 摄像机,收尾了 NASA JPL 早期开发 CMOS 本事的甘愿(Fossum 2023)。

一、制造本事的朝上

从当代 CMOS 图像传感器问世到今天,制造本事的朝上进一步提高了 CIS 的性能。

1、大限度坐蓐背照式图像传感器。

自从转移电话和智高手机安装了摄像头之后,对微型、高永别率摄像头的需求变得越来越高,因此有必要进一步减轻像素尺寸,在给定镜头 F 数的情况下减少像素的集光。为了在不葬送 PD 面积比的情况下减轻像素尺寸,科学界经受了后头照明本事(Iwabuchi 等东说念主,2006 年;Rhodes 等东说念主,2009 年;Wuu 等东说念主,2009 年)。现时,很多 CMOS 图像传感器都经受 BSI 决议。图 8 展示了 FSI 和 BSI 像素截面图。后头照明的优点是填充因子大,从硅到微透镜的堆叠高度小,而且不错解放选拔金属层数和金属布局。因此,像素的灵巧度大大提高。

图 8 :(a) 正面发光像素和 (b) 后头发光(BSI)像素的示例,线路 BSI 像素具有更好的聚光武艺。

BSI 图像传感器的制作经由如下:(1) 正面处理,包括布线;(2) 通过平直键合将晶圆与撑握晶圆键合;(3) 薄化传感器晶圆;(4) 后头处理以阻碍暗电流;(5) 抗反射涂层;(6) 彩色滤光片应用;(7) 微型透镜应用;以及 (8) 键合垫开孔。在第二步中,将传感器晶圆和撑握晶圆压平并清洗;用等离子体活假名义;终末将两个晶圆战役并退火。第三步,在减薄经由的终末阶段,为赢得精准和均匀的厚度,经受化学机械抛光。

2、深沟顽固。

现时可能的最小像素尺寸约为 0.5 μm,而具有深奥可见光继承武艺的最小实用硅厚度约为 4 μm。因此,像素尺寸与硅厚度的纵横比高达 8,这就形成了光学串扰和电子扩散串扰。为了减少串扰,东说念主们引入了深沟顽固(DTI)本事(Park 等东说念主,2007 年)。电介质、多晶硅和钨都不错埋入 DTI 中。电子扩散串扰被 DTI 阻断。填充金属的 DTI 能完全阻碍光学串扰,而含有电介质和多晶硅的 DTI 则能在一定进度上减少串扰。

DTI 经受博世工艺进行高光谱沟槽蚀刻(Roozeboom 等东说念主,2015 年)。为了阻碍来自 DTI 接口的暗电流,经受了三种方法。第一种是通过等离子体掺硼在 DTI 名义形成 p+ 层(Moon 等东说念主,2007 年)。在这种情况下,很多材料都可用作填充物。第二种方法是埋入带负电的介电材料,从而将空穴蛊惑到界面上。第三种方法是在名义形成一层薄薄的介电层,行为栅介质,并千里积多晶硅或钨行为栅极。在多晶硅或金属上施加负偏压以积聚空穴(Kitamura 等东说念主,2012 年;Ahn 等东说念主,2014 年)。

3、三维堆叠本事。

三维堆叠本事可将包括图像处理在内的功能集成到 CMOS 图像传感器中,从而收尾微型、高性能的智能相机。逻辑电路晶圆是一种铜-铜搀杂晶圆,粘合在图像传感器晶圆上(Sukegawa 等东说念主,2013 年;Oike,2022 年)(图 9)。两个晶圆通过 SiO2-SiO2 和 Cu-Cu 进行物理粘合,并在外围区域和/或像素区域进行电气团结(Kagawa 等东说念主,2016 年)。逻辑晶圆经受相宜的细致工艺本事,以收尾多样功能的高速运行和低功耗耗散。哄骗硅通孔收尾晶圆之间的电气团结,开发出了由图像传感器晶圆、动态立时存取存储器(DRAM)晶圆和逻辑晶圆构成的三层堆栈(Haruta 等东说念主,2017 年)。DRAM 以较大的带宽团结到逻辑晶圆中的图像处理器。

图 9 :(a) 后头发光器件和 (b) 三维堆叠图像传感器(基层用于附加电路)的横截濒临比久了图。

二、特定应用界限的朝上

当代固态图像传感器的潜在应用似乎取之不尽。时于当天,险些每天都有新的应用出现。固然转移成像在很猛进度上推动了 CIS 业务本事的发展,但有几种特定应用需要经受与转移成像传感器不同的专用联想、布局或制造本事。本节将研究其中几种应用。

1、汽车高动态范围。

从交易角度看,汽车行业是 CIS 系统最有出路的新兴商场之一。固然某些性能参数与汽车应用无关,但高动态范围是一个重要要求。消费类斥地在莫得特殊计划的情况下,动态范围可达 80-90 dB,但汽车成像要求动态范围至少达到 120 dB。本事文献中报说念了几种提高 CIS 动态范围的本事,但其中一些本事会产生认知伪影,而自动驾驶汽车需要幸免这种伪影。

汽车界限的另一个垂死问题是要求成像部件对汽车和交通秀雅光源中的 LED 能干不敏锐。要减缓 LED 能干,需要经受复杂的方法(Takayanagi 和 Kuroda,2012 年)。

意法半导体(ST Microelectronics)发布了一款可交代 LED 能干的图像传感器(Tournier 等东说念主,2018 年),该传感器可产生无认知伪影的宽动态范围输出信号。该器件使用两个具有斩波曝光的 PD。第一个 PD 使用屡次万古辰曝光,光产生的电荷累积在第一个存储电容器上。第二个光电休养器哄骗屡次较短的曝光时辰,将光生电荷累积到第二个存储电容器上。屡次长曝光时辰和屡次短曝光时辰交错进行,因此最终驱散是两者的组合。这种组合的脾气是动态范围宽,莫得认知伪影,也莫得 LED 能干问题。

2、医用和胶囊内窥镜。

内窥镜的一个典型要求是外形工整,因为摄像头需要穿过东说念主体的狭窄启齿。通过将电子电路彭胀集成到一块硅片上,并尽量减少芯片外部的引线数目,就能收尾小尺寸图像传感器。在这类应用中,需要不越过四个 I/O 引脚的器件。这些斥地在 CCD 期间就有了,但用于驱动和读出 CCD 的完整外围电路并莫得集成在芯片上,而是位于东说念主体外部并通过导线团结。

在胶囊内窥镜查验的顶点情况下,药丸相机被病东说念主吞下并通过完整的胃肠说念(Iddan 和 Swain,2003 年)。这就意味着,胶囊内不仅要有带 ISP 的传感器,还要有镜头、光源、电板和射频传输电子元件(每 8 秒向外界传输一帧图像)。此外,扫数这个词系统还必须粗略使用自带的微型电板职责多个小时。Photobit 公司开发并坐蓐了一种定制的超低功耗 CIS。这是使用与其他 CMOS 电子元件集成在一齐的 CMOS 图像传感器收尾微型化的一个顶点而垂死的例子。

3、高速率。

片上集成与堆叠本事相结合,相等妥贴高速应用,因为不错并行处理和处理信号。举例,将全局 ADC 休养为列级 ADC 不错提高图像传感器的最大帧频,因为列级休养的并行性减少了串行全局 ADC 的耗时休养。需要防卫的是,一个 ADC 也不错干事于多个列(Chen 等东说念主,1990 年)。从列级 ADC 休养为像素级 ADC 不错进一步提高斥地的最大帧频(Kleinfelder 等东说念主,2001 年)。就速率而言,ADC 的休养时辰可能是一个驱散身分,除此以外,另一个相等垂死的时辰驱散身分是将扫数生成的比特都置于片外。同期输出多个像素的数字代码需要并行处理。这将加多斥地封装上的引脚数目,并相应加多封装资本。在某些情况下,封装资本可能高于裸芯片的资本。

通过以上研究,咱们不错得出这么的论断:像素级 ADC 是高速图像传感器的首选。然则,在每个像素中都安装 ADC 会大大裁汰像素的填充整个。这个问题不错通过改用堆叠式科罚决议来科罚;顶层包含图像传感部分,底层包含 ADC(Takahashi 等东说念主,2018 年)。经受特意的三维堆叠结构,图像传感器的性能已越过 100-Mfps(连拍模式)(Kuroda 等东说念主,2019 年)。

4、科学成像

科学成像界限极为庸俗,包括很多细分商场,如天际应用、天文成像、高能粒子探伤以及扫描和透射电子束显微镜应用(SEM 和 TEM)的电子探伤。在扫数这些应用中起垂死作用的一个共同参数是对低噪声性能的严格要求。噪声不仅决定了图像传感器的信噪比和动态范围,还决定了为赢得可接受的输出驱散所需的最小输入信号。

降噪研究从第一台 CCD 制造出来的那一刻起就运行了,于今还是 CIS 界的热点话题。除了在坐蓐经由中引入新的要领(如优化氧化经由、暗电流裁汰要领),像素的联想和布局(如 PPD、垂直 TG、钝化层)以及模拟电路(如电荷域 CDS、辩论多重采样)也受到了庸俗真贵(Chen 等东说念主,2012 年;Ge & Theuwissen,2017 年)。一朝读取噪声水平达到 0.3 e- r.m.s.,以致低至 0.15 e- r.m.s.,就能以深奥或极高的精度驯顺电子数(Teranishi,2012 年;Fossum,2013 年 b)。在 CMOS 图像传感器的早期,40 e- r.m.s. 的噪声水平并不特等。如今,室温操作下的平均读取噪声值已低于 0.20 e- r.m.s.(Ma 等东说念主,2021a, 2022a),从而收尾了超低照度成像应用。

5、动态视觉传感器。

在机器视觉视频应用中,在单元时辰内会拿获多量图像。在许厚情况下,这些图像包含的多量信息在不同图像之间不会发生变化。然则,不管图像内容若何,传感器生成的每一帧图像都需要读出。在动态视觉传感器(DVS)中,帧与帧之间冗余信息的存在被用来加速斥地运行速率和/或减少输出数据量。DVS 的主张相对浮浅:斥地的输出只线路两幅连气儿图像之间的变化(Dickinson 等东说念主,1995 年;Delbrück 等东说念主,2010 年)。每个像素都会捕捉曝光时辰内的信息,并将驱散与上一次曝光时辰内赢得的输出进行比较。如果两个连气儿曝光时辰之间莫得变化,则像素不会发送任何信息。如果连气儿两幅图像之间存在各别(越过特定阈值),像素就会运行职责,并敷陈其位置、发现各别的时辰,以及两幅图像之间的各别是正(信号加多)照旧负(信号减少)。换句话说,像素检测的是帧与帧之间对比度的变化。大多数情况下,使用的是对数反应的像素。

DVS 的输出不是一张雅瞻念的图像,而是一个数字信息流,线路在哪个位置和哪个时辰点不雅察到光强的负或正变化。最近的趋势是将 DVS 与措施 RGB CMOS 传感器相结合;DVS 斥地的输出可用于立异 RGB 数据中的认知伪影(Guo 等东说念主,2023 年;Kodama 等东说念主,2023 年)。

6、波折遨游时辰测距图像传感器。

波折遨游时辰(iToF)图像传感器用于通过二维成像系统测量三维尺寸(或距离)。光源发出近红外光脉冲(如占空比为 50%),传感器试图检测光脉冲在物体上反射后复返的光信号。摄像机与物体之间的距离不错通过浮浅的蓄意得出。蓄意方法基于光源开启阶段传感器检测到的光量测量值与光源关闭阶段传感器检测到的光量测量值之间的比率(Kim 等东说念主,2010 年)。相机与物体之间的距离越短,在光源开启阶段麇集到的信号就越多。摄像机与物体之间的距离越长,在关断阶段麇集到的信号就越多。由于光速相等快,因此像素在 "开 "和 "关 "阶段之间的切换也需要很快。像素的曝光时辰为纳秒级。由于在如斯短的曝光时辰内麇集到的信号相等小,因此像素中会累积多个测量值,并存储在像素内的电容器中(Kawahito,2021 年)。

iToF 像素的职责模式要求高速麇集光生电子,并超快地将电荷包从 PPD 传输到存储节点。要在数百兆赫兹的调制频率下运行这些像素,很是的漂移场(通过奥秘的联想和布局产生)是十足必要的(Xu 等东说念主,2016 年)。

三、量子图像传感器

2005 年,有东说念主提倡了一种不同的图像传感器方法,即由多量以高帧频运行的专用狭窄像素(称为 jots)对单光子进行检测和计数(Fossum,2005 年)。1 检测基本上是二进制的:0 久了莫得光子,1 久了有光子。多帧二进制数据可用来再现灰度图像,如图 10 所示。单光子灵巧度意味着不错在最暗的光辉下成像。这一主张领先被称为数字薄膜传感器,自后改名为量子图像传感器(QIS),并彭胀到多比特操作(Fossum 等东说念主,2016 年)。

图 10 :量子图像传感器主张图,线路了点阵输出的空间散播(左图)、不同期间片的点阵输出位平面张开图(中图)以及由点阵时空邻域形成的灰度图像像素(右图)。图改编自 Ma 等东说念主(2022a)。

1、哄骗单光子雪崩探伤器收尾量子图像传感器。

单光子雪崩探伤器(SPAD)安装由于哄骗高电场和撞击电离赢得载流子,因此对单光子相等敏锐。哄骗 SPAD 阵列,研究小组已运行展示 QIS 主张并诠释成像特征模子(Dutton 等东说念主,2015 年)。2021 年,初度报说念了像素间距为 6.4μm 的 3.2-Mpixel SPAD 阵列(Morimoto 等东说念主,2021 年)。由于 SPAD 依靠雪崩倍增赢得信号增益,因此需要较高的里面电场和相对较大的像素间距来确保顽固,而且往交往可能具有较高的暗计数率(暗电流)。尽管存在这些问题,但 SPAD 已被诠释对 3D 成像等快速光子到达定时应用相等有用。SPAD 本事还哄骗了 CMOS 图像传感器的本事,如三维堆叠(Ito 等,2020 年)和低暗电流结构。

2、互补金属氧化物半导体量子图像传感器。

收尾 CMOS QIS 的职责始于 2012 年的达特茅斯大学。那时,由于 SPAD 像素相等大、需要高电压和高暗电流率,因此 SPAD 方法被否决。这种方法不使用雪崩增益来检测单个光电子,而是通过使用很小的感应节点电容来赢得增益,从而产生 300-500 μV/e- 范围内的 CG。通过像素内电荷革新,革新到该电容上的单个电子可产生远高于输入参考本底噪声(举例 0.2 e- r.m.s. 本底噪声)的可辨信号,因此单个光电子的检测谬误率较低。检测经由比 SPAD 慢,但不错收尾亚微秒级定时。由于 CMOS QIS 不需要 SPAD 的高电场,因此不错收尾更小的像素或点阵,并提高了可制造性,从而裁汰了单元像素的资本和光学器件的体积。功率耗散也大大裁汰。图 11 展示了泵栅点器件。图 12 展示了室温光电子数永别率的实验考据。

图 11 :具有超低感测节点电容的泵栅 jot 器件。(a) BSI 像素的横截面。(b) 沿像素内电荷革新旅途的静电势。面板改编自 Ma & Fossum (2015)。缩写:BSI,后头发光;FD,浮动扩散;PB,p 型体硅;PW,p 型阱;SW,存储阱;TG,革新栅;VB,编造势垒。

图 12 :测量到的光子计数直方图(出现次数与归一化读出电压的关系),线路出显着的光电子量化。峰高对应于平均光电子到达率 H 为 2.1 e-/样品的泊松散播,峰宽则与残余读出噪声联系。图改编自 Ma 等东说念主(2017)。

2017 年,达特茅斯大学敷陈了一款室温下的 1-Mpixel QIS 器件,该器件经受近乎措施的 BSI CIS 3D 叠层工艺收尾,像素间距为 1.1μm,职责频率为 1,000 fps,总功耗约为 20 mW(Ma 等东说念主,2017 年)。1-Mpixel QIS 的展示比第一个 1-Mpixel SPAD 阵列早两年多,像素也小得多。轻视 34 个 1.1μm 像素的 CMOS QIS 可容纳一个 6.4μm 像素的 SPAD。最近,经受 QIS 光子计数本事的 CMOS 图像传感器收尾了高动态范围和 163-M 像素永别率(Ma 等,2021b;2022b)。现时正在探索 QIS 本事的应用,包括用于安全、国防、科学和其他应用的低照度成像。CIS QIS 本事和 SPAD QIS 本事都占据了垂死的应用界限(Ma 等东说念主,2022a),并引发了低照度图像和视频捕捉界限的蓄意成像研究(如 ICCP 2023)。

四、固态图像传感器的新界限

在本节中,咱们将研究一些引起图像传感器界风趣的新兴本事。

三维堆叠本事提高了传感器的集成度,收尾了高密度焦平面图像处理,提高了隐约量,同期裁汰了系统功耗(Fossum,1989 年)。能以大限度并行风物进行的蓄意可能会从三维堆叠中获益最多,而计划到团结性,腹舆图像处理可能比全局图像处理获益更多。现时正在哄骗三维堆叠本事探索具有边际蓄意功能的智能相机(Eki 等,2021 年)。

光子计数图像传感器在往日五年中发展飞速,并收尾了新的应用。这项本事很可能在不久的将来成为主流 CIS 本事的一部分,从而收尾更大的动态范围和弱光成像的终极性能,终点是与蓄意成像相结合时(Ma 等,2022b)。

超大尺寸视频图像传感器仍在为专科商场而开发。举例,在拉斯维加斯的 Sphere 千里浸式影院中就使用了一个 316-Mpixel 120-fps 的传感器(Agarwal 等,2023 年)。

最近,硅读出集成电路上的薄膜晶体管图像传感器与量子点光电探伤器相结合,提高了成像性能。这些传感器在短波和近红外波段的反应速率也比硅探伤器更好(Kim 等东说念主,2023 年)。

图像认证是一个日益受到真贵的界限,尤其是当社会参加一个哄骗东说念主工智能本事莽撞生成传神但纰谬图像的期间。东说念主们正在探索更安全的方法来确保原始图像数据的完整性(Mansoorian & Fossum 2002,Fowler 等东说念主,2023 年)。

在光学方面,跟着所谓的齐备颜色路由器(Catrysse 等,2022 年)的开发,从拜耳红、绿、蓝、绿(RGBG)颜色滤镜内核到接收每个像素点的 R、G、B 信号(从而幸免颜色混叠问题,这是图像传感器界长期以来的逸想)的可能性似乎正在接近现实。金属透镜偏激片上集成的辩论发展可能会简化相机联想,并减小相机的尺寸和分量(Khorasaninejad 和 Capasso,2017 年)。

论断

固态图像传感器不停发展,在咱们的日常生涯中无处不在。不仅个东说念主不错与家东说念主和一又友一齐观赏像片和视频,而且每个东说念主都不错在外交媒体上看到它们。这影响了商场、文化、素养以致政事。在机器视觉、无东说念主机、条形码阅读器、生物识别和手势识别等界限,蓄意机而非东说念主类看到图像的商场也在不停增长。有些应用需要检测 X 射线、红外线和带电粒子。此外,测距、偏振和相位(波前)成像武艺的不停提高也带来了新的应用。

就像人所共知的双刃剑雷同,图像传感器本事的发展也带来了新的社会问题,而不单是是不言而谕的外交媒体问题。这些问题包括:哄骗摄像头为不法活动提供便利(如偷窥、违警摄像、身份盗窃);滋扰隐秘权,包括专制政府机构的自动面部识别和追踪;以及克扣未成年东说念主和分享违警色情图片。关于一项旨在以光明和真义造福个东说念主福祉和扫数这个词社会的本事而言,咱们还必须想到和限制剑的黯淡边际,这如实令东说念主缺憾。

原文团结

https://www.annualreviews.org/content/journals/10.1146/annurev-vision-101322-105538

本文来自微信公众号"半导体行业不雅察"(ID:icbank)体育游戏app平台,作家:Fossum等,36氪经授权发布。